US 20140347401A1

(19) **United States**

(12) **Patent Application Publication**

HWANG et al.

(10) **Pub. No.: US 2014/0347401 A1**

(43) **Pub. Date: Nov. 27, 2014**

(54) **PIXEL, DISPLAY DEVICE COMPRISING THE SAME AND DRIVING METHOD THEREOF**

(71) Applicant: **Samsung Display Co., Ltd.**, Yongin-city (KR)

(72) Inventors: **YOUNG-IN HWANG**, Yongin-city (KR); **Yong-Jin Cho**, Yongin-city (KR)

(73) Assignee: **Samsung Display Co., Ltd.**, Yongin-city (KR)

(21) Appl. No.: **14/029,686**

(22) Filed: **Sep. 17, 2013**

(30) **Foreign Application Priority Data**

May 27, 2013 (KR) ..... 10-2013-0059847

#### Publication Classification

(51) **Int. Cl.**

**G09G 3/32**

(2006.01)

(52) **U.S. Cl.**

CPC ..... **G09G 3/3233** (2013.01)

USPC ..... **345/690; 345/82**

#### (57) **ABSTRACT**

A display device and a driving method thereof are disclosed. In one aspect, the display device includes a plurality of pixels, each including a driver which generates a driving current according to an input image data signal and a light emission portion formed of an organic light-emitting diode which emits light according to the driving current and at least one dummy pixel connected to a repair line that is connected to a light emission portion of at least one first pixel among the plurality of pixels. The dummy pixel includes a dummy pixel driver having the same structure as the drivers of each of the plurality of pixels, a dummy pixel light emission portion formed of an organic light-emitting diode, and a repair driver which transmits a driving current generated in the dummy pixel driver through the repair line when a driver of the first pixel fails.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

## PIXEL, DISPLAY DEVICE COMPRISING THE SAME AND DRIVING METHOD THEREOF

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims priority to and the benefit of Korean Patent Application No. 10-2013-0059847 filed in the Korean Intellectual Property Office on May 27, 2013, the entire contents of which are incorporated herein by reference.

### BACKGROUND

#### [0002] 1. Field

[0003] The described technology generally relates to a pixel, a display device including the pixel, and a method for driving the display device.

#### [0004] 2. Description of the Related Technology

[0005] Organic light-emitting diode (OLED) displays generally display images by using self-emissive OLEDs. The luminance of OLEDs is controlled by a current or voltage supplied thereto.

[0006] In general, OLED displays are classified as either passive matrix type OLEDs (PMOLED) or active matrix type OLEDs (AMOLED) according to driving mechanism.

[0007] AMOLEDs select every unit pixel when displaying light and typically have high resolution, contrast, and operation speeds.

[0008] In AMOLED displays, each pixel typically includes a driving transistor which controls the current supplied to the OLED, and the OLED emits light corresponding to the driving current in accordance with a data signal input through the driving transistor.

[0009] However, such pixel circuits may be complex and thus manufacturing these circuits is complicated. Thus, the manufacturing yield may be decreased as the size and resolution of the display device is increased.

[0010] Therefore, if a defective pixel is made during the typical manufacturing process, a repair process should be performed in order to utilize the pixel.

[0011] The above information disclosed in this Background section is only intended to facilitate understanding of the background of the described technology and therefore it may contain information that does not constitute the prior art that is already known in this country to a person of ordinary skill in the art.

### SUMMARY OF CERTAIN INVENTIVE ASPECTS

[0012] One inventive aspect is to increase the manufacturing yield of an OLED display by repairing defective pixels so that they may operate as normal pixels through a repairing process and thus improve the screen quality or product quality deterioration of the OLED display.

[0013] Another aspect is a pixel structure that enables the repair of a defective pixel, an OLED display device that can control a repair process according to a driving method of the OLED display device, and a method for driving the same.

[0014] Another aspect is a display device comprising: a plurality of pixels, each including a driver generating a driving current according to an input image data signal and a light emission portion formed of an organic light-emitting diode emitting light according to the driving current; and at least one dummy pixel electrically connected to a repair line that is electrically connected to a light emission portion of at least one first pixel among the plurality of pixels. The dummy pixel

includes: a dummy pixel driver having the same structure as the driver of each of the plurality of pixels, a dummy pixel light emission portion formed of an organic light-emitting diode, and a repair driver transmitting a driving current generated by the dummy pixel driver through the repair line when the driver of the first pixel has failed.

[0015] The repair driver may include: a first repair transistor turned on during a light emission period of the plurality of pixels to electrically connect the dummy pixel driver to the repair line; a second repair transistor provided between the dummy pixel driver and the dummy pixel light emission portion and being turned on during a non-light emission period of the plurality of pixels and being turned off during the light emission period of the plurality of pixels; and a third repair transistor turned on during a predetermined period before the light emission period of the plurality of pixels to apply an initialization driving voltage to the repair line.

[0016] The first repair transistor may include a gate electrode electrically connected to a first repair control line transmitting a first repair control signal, a first electrode electrically connected to the dummy pixel driver, and a second electrode electrically connected to the repair line.

[0017] The driver of each of the plurality of pixels and the dummy pixel driver may each respectively include: a driving transistor, including a gate electrode electrically connected to a first node, a first electrode electrically connected to a first power source voltage, and a second electrode electrically connected to a third node; a switching transistor, including a gate electrode electrically connected to the corresponding scan line which receives a scan signal, a first electrode electrically connected to the corresponding data line, and a second electrode electrically connected to a second node; a compensation transistor, including a gate electrode electrically connected to a first control line which receives a first control signal, a first electrode electrically connected to the first node, and a second electrode electrically connected to the third node; a storage capacitor, including a first electrode electrically connected to the first power source voltage and a second electrode electrically connected to the second node; and a compensation capacitor, including a first electrode electrically connected to the first node and a second electrode electrically connected to the second node.

[0018] The driver of each of the plurality of pixels and the dummy pixel driver are controlled by a voltage level of the first power source voltage and a voltage level of a second power source voltage electrically connected with an organic light-emitting diode of each of the plurality of pixels and a cathode of an organic light-emitting diode in the dummy pixel.

[0019] While the first power source voltage is applied as a predetermined high level voltage and the second power source voltage is applied as a predetermined low level voltage, the organic light-emitting diodes of the respective pixels substantially simultaneously emit light and the organic light-emitting diode of the dummy pixel does not emit light.

[0020] Another aspect is the driver of each of the plurality of pixels and the dummy pixel driver may each respectively include: a switching transistor, including a gate electrode electrically connected to the corresponding scan line which receives a scan signal, a first electrode electrically connected to the corresponding data line, and a second electrode electrically connected to a fourth node; a compensation transistor, including a gate electrode electrically connected to a first control line which receives a first control signal, a first elec-

trode electrically connected to the first node, and a second electrode electrically connected to the third node; a relay transistor, including a gate electrode electrically connected to a second control line which receives a second control signal, a first electrode electrically connected to the fourth node, and a second electrode electrically connected to a second node; a sustain transistor, including a gate electrode electrically connected to the first control line, a first electrode electrically connected to the corresponding data line, and a second electrode electrically connected to the second node; a storage capacitor, including a first electrode electrically connected to the first power source voltage and a second electrode electrically connected to the second node; a compensation capacitor, including a first electrode electrically connected to the first node and a second electrode electrically connected to the second node; and a sustain capacitor, including a first electrode electrically connected to the fourth node and a second electrode electrically connected to a power supply transmitting a predetermined reference voltage.

[0021] The driver of each of the plurality of pixels and the driver of the dummy pixel driver are controlled by a voltage level of the first power source voltage and a voltage level of a second power source voltage electrically connected with an organic light-emitting diode of each of the plurality of pixels and a cathode of an organic light-emitting diode of the dummy pixel.

[0022] While the first power source voltage is applied as a predetermined high level voltage and the second power source voltage is applied as a predetermined low level voltage, the organic light-emitting diodes of the respective pixels substantially simultaneously emit light and the organic light-emitting diode of the dummy pixel does not emit light.

[0023] In addition, while the first power source voltage is applied as a predetermined high level voltage and the second power source voltage is applied as a predetermined low level voltage, scan signals corresponding to the gate electrodes of the switching transistors of the respective drivers of the plurality of pixels and the dummy pixel driver are sequentially applied with a gate on voltage level.

[0024] Another aspect is the drivers of the plurality of pixels and the dummy pixel driver may each respectively include: a driving transistor, including a gate electrode electrically connected to a first node, a first electrode electrically connected to a first power source voltage, and a second electrode electrically connected to a third node; a switching transistor, including a gate electrode electrically connected to the corresponding scan line which receives a scan signal, a first electrode electrically connected to a power supply applying a predetermined reference voltage, and a second electrode electrically connected to a fourth node; a compensation transistor, including a gate electrode electrically connected to a first control line which receives a first control signal, a first electrode electrically connected to the first node, and a second electrode electrically connected to the third node; a relay transistor, including a gate electrode electrically connected to a second control line which receives a second control signal, a first electrode electrically connected to the fourth node, and a second electrode electrically connected to a second node; a sustain transistor, including a gate electrode electrically connected to a third control line which receives a third control signal, a first electrode electrically connected to the first power source voltage, and a second electrode electrically connected to the second node; a storage capacitor, including a first electrode electrically connected to the first node and a

second electrode electrically connected to the second node; and a sustain capacitor, including a first electrode electrically connected to the corresponding data line and a second electrode electrically connected to the fourth node.

[0025] In this case, the driver of each of the plurality of pixels and the dummy pixel driver are controlled by a voltage level of the first power source voltage and a voltage level of a second power source voltage electrically connected with an organic light-emitting diode of each of the plurality of pixels and a cathode of an organic light-emitting diode of the dummy pixel.

[0026] Another aspect is a display device comprising: a display unit including the plurality of pixels and the at least one dummy pixel; a scan driver transmitting a plurality of scan signals corresponding to the plurality of pixels and the at least one dummy pixels; a data driver transmitting a plurality of image data signals corresponding to the plurality of pixels and the at least one dummy pixel; a power supply supplying a plurality of power source voltages and a predetermined reference voltage for driving of the plurality of pixels and the at least one dummy pixel; a compensation control signal unit transmitting a plurality of control signals that control operations of the drivers of the plurality of pixels and the dummy pixel driver; a repair control signal unit transmitting a plurality of repair control signals that control operation of the repair driver; and a signal controller generating and transmitting a plurality of driving control signals that control the scan driver, the data driver, the power supply, the compensation control signal unit, and the repair control signal unit, processing an external image signal, and transmitting the image data signal to the data driver.

[0027] Another aspect is a pixel comprising: a first driver including a driving transistor generating a driving current according to an image data signal, a switching transistor activating an external pixel corresponding to a scan signal, a compensation transistor compensating for a threshold voltage of the driving transistor, a storage capacitor storing a voltage corresponding the image data signal, and a compensation capacitor storing the threshold voltage of the driving transistor during a predetermined period; a first light emission portion including an organic light-emitting diode; and a repair driver provided between a first electrode of the driving transistor and a repair line electrically connected to an organic light-emitting diode of an external pixel, and including a first repair transistor transmitting a driving current to the organic light-emitting diode of the external pixel, a second repair transistor formed between the first driver and the first light emission portion, and a third repair transistor electrically connected to the first driver by diode-connecting a gate electrode and a first electrode of the third repair transistor and applying an initialization driving voltage to the repair line.

[0028] Another aspect is a pixel comprising: a second driver including a driving transistor generating a driving current according to an image data signal, a switching transistor activating an external pixel corresponding to a scan signal, a compensation transistor compensating for a threshold voltage of the driving transistor, a relay transistor transmitting a voltage corresponding to a data voltage of the previous frame, a sustain transistor transmitting a predetermined voltage applied through the corresponding data line in substantial synchronization with a switching operation of the compensation transistor, a sustain capacitor storing a voltage corresponding to a data voltage of the present frame corresponding to the switching operation of the switching transistor, a stor-

age capacitor storing a voltage corresponding to a data voltage of the previous frame received from the relay transistor, and a compensation capacitor storing the threshold voltage of the driving transistor; a second light emitting portion including an organic light-emitting diode; and a repair driver provided between a first electrode of the driving transistor and a repair line electrically connected to an organic light-emitting diode of an external pixel, and including a first repair transistor transmitting a driving current to the organic light-emitting diode of the external pixel, a second repair transistor formed between the second driver and the second light emission portion, and a third repair transistor electrically connected to the second driver by diode-connecting a gate electrode and a first electrode of the third repair transistor and applying an initialization driving voltage to the repair line.

[0029] Another aspect is a pixel comprising: a third driver including a driving transistor generating a driving current according to an image data signal, a switching transistor activating an external pixel corresponding to a scan signal, a compensation transistor compensating for a threshold voltage of the driving transistor, a relay transistor transmitting a voltage corresponding to a data voltage of the previous frame, a sustain transistor transmitting a first power source voltage to a gate electrode terminal of the driving transistor, a sustain capacitor receiving and storing a voltage corresponding to a data voltage of the previous frame through the corresponding data line, and storage capacitor storing a voltage corresponding to a data voltage of the previous frame transmitted through the relay transistor; a third light emission portion including an organic light-emitting diode; and a repair driver provided between a first electrode of the driving transistor and an organic light-emitting diode of an external pixel, and including a first repair transistor transmitting a driving current to the organic light-emitting diode of the external pixel, a second repair transistor formed between the third driver and the third light emission portion, and a third repair transistor electrically connected to the third driver by diode-connecting a gate electrode and a first electrode of the third repair transistor and applying an initialization driving voltage to the repair line.

[0030] Another aspect is a method for driving a display device including a plurality of pixels and at least one dummy pixel. Each of the plurality of pixels includes an organic light-emitting diode, a driving transistor generating a driving current according to an image data signal, a switching transistor responding to a scan signal, a compensation transistor compensating for a threshold voltage of the driver transistor, a storage capacitor storing a voltage corresponding to the image data signal, and a compensation capacitor storing the threshold voltage of the driving transistor, and the at least one dummy pixel has the same structure as the plurality of pixels and includes a repair driver electrically connected with a repair line that is electrically connected to an organic light-emitting diode of a pixel among the plurality of pixels.

[0031] The method for driving the display device includes: applying a first voltage to a gate electrode of the driving transistor through the corresponding data line; resetting a voltage of a drain electrode of the driving transistor to a low-level first power source voltage; compensating for the threshold voltage of the driving transistor by turning on the compensation transistor; transmitting a voltage according to the image data signal through the corresponding data line in response to the corresponding scan signals sequentially transmitted through the switching transistors of each of the plurality of pixels and the dummy pixel and storing the voltage in

the storage capacitor; and applying a low-level second power source voltage to a cathode of the organic light-emitting diode such that organic light-emitting diodes of the plurality of pixels substantially simultaneously emit light in accordance with the driving current.

[0032] The repair driver of the dummy pixel includes a first repair transistor transmitting a driving current generated from the driving transistor of the dummy pixel to the repair line, and the first repair transistor is turned on when the organic light-emitting diodes of the plurality of pixels substantially simultaneously emit light.

[0033] The repair driver of the dummy pixel further includes a second repair transistor provided between the driving transistor of the dummy pixel and an organic light-emitting diode of the dummy pixel, the second repair transistor is turned on in the applying of the first voltage, the resetting, the compensating, and the scanning, and the second repair transistor is turned off in the substantially simultaneous light emission of the organic light-emitting diodes.

[0034] The repair driver of the dummy pixel further includes a third repair transistor of which a first electrode of the third repair transistor is electrically connected to a node of the driving transistor of the dummy pixel and the repair line, and a gate electrode and a second electrode of the third repair transistor are electrically connected to each other, and the third repair transistor is turned on during a predetermined period before the substantially simultaneous light emission to apply an initialization driving voltage to the repair line.

[0035] Another aspect is a method for driving a display device including a plurality of pixels and at least one dummy pixel. Each of the plurality of pixels includes an organic light-emitting diode, a driving transistor generating a driving current according to an image data signal, a switching transistor responding to a scan signal, a compensation transistor compensating for a threshold voltage of the driving transistor, a relay transistor transmitting a data voltage of the previous frame to a gate electrode terminal of the driving transistor, a sustain capacitor programming and storing a data voltage of the present frame received from the corresponding data line, and a storage capacitor storing a voltage corresponding to the data voltage of the previous frame, and the dummy pixel has the same structure as the plurality of pixels and includes a repair driver electrically connected to a repair line that is electrically connected to an organic light-emitting diode of at least one pixel of the plurality of pixels.

[0036] The method for driving the display device includes: resetting a voltage of a drain electrode of the driving transistor to a low-level first power source voltage; compensating for the threshold voltage of the driving transistor by turning on the compensation transistor; transmitting a data voltage of the previous frame stored in the sustain capacitor to the gate electrode terminal of the driving transistor by turning on the relay transistor; substantially simultaneously emitting light from the organic light-emitting diodes of the plurality of pixels with in accordance with the driving current according to the data voltage of the previous frame by applying a low-level second power source voltage to a cathode of the organic light-emitting diode; and turning on the switching transistors for each of the plurality of pixels and the dummy pixel according to sequentially transmitted scan signals substantially at the same time as the substantially simultaneous light emission, and storing the data voltage of the present frame applied through the corresponding data line.

[0037] The repair driver of the dummy pixel includes a first repair transistor transmitting a driving current generated from the driving transistor of the dummy pixel to the repair line, and the first repair transistor is turned on in the substantially simultaneous light emission.

[0038] The period of the substantially simultaneous light emission may be longer than or equal to the period of the scanning, and the substantially simultaneous light emission and the scanning may be substantially at the same time in each of the plurality of pixels and the dummy pixel.

[0039] The repair driver of the dummy pixel further includes a second repair transistor provided between the driving transistor of the dummy pixel and an organic light-emitting diode of the dummy pixel, the second repair transistor is turned on in the resetting, the compensating, and the transmitting, and the second repair transistor is turned off in the substantially simultaneous light emission and the scanning.

[0040] The repair driver of the dummy pixel further includes a third repair transistor of which a first electrode of the third repair transistor is electrically connected to a node of the driving transistor of the dummy pixel and the repair line and a gate electrode and a second electrode of the third repair transistor are electrically connected to each other, and the third repair transistor is turned on during a predetermined period before the substantially simultaneous light emission to apply an initialization driving voltage to the repair line.

[0041] According to at least one embodiment, a pixel structure that can repair a defective pixel and a display device including the pixel structure are provided to thereby perform a repair process appropriate for a driving method in the display device and improve a manufacturing yield of the display device by recovering the functionality of the defective pixel to that of a normal pixel.

[0042] In addition, according to at least one embodiment, a luminance deviation due to the difference in operation between a repair pixel that recovers the functionality of a defective pixel according to a driving method of the display device and a normal pixel can be improved, thereby improving the productivity of the display device in order to have an excellent screen display quality.

#### BRIEF DESCRIPTION OF THE DRAWINGS

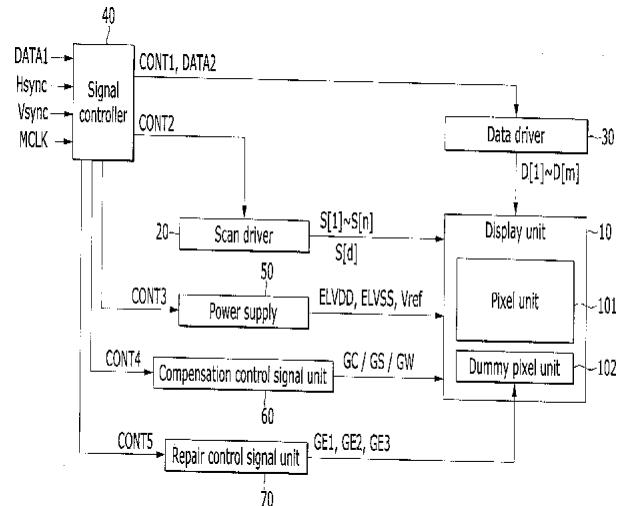

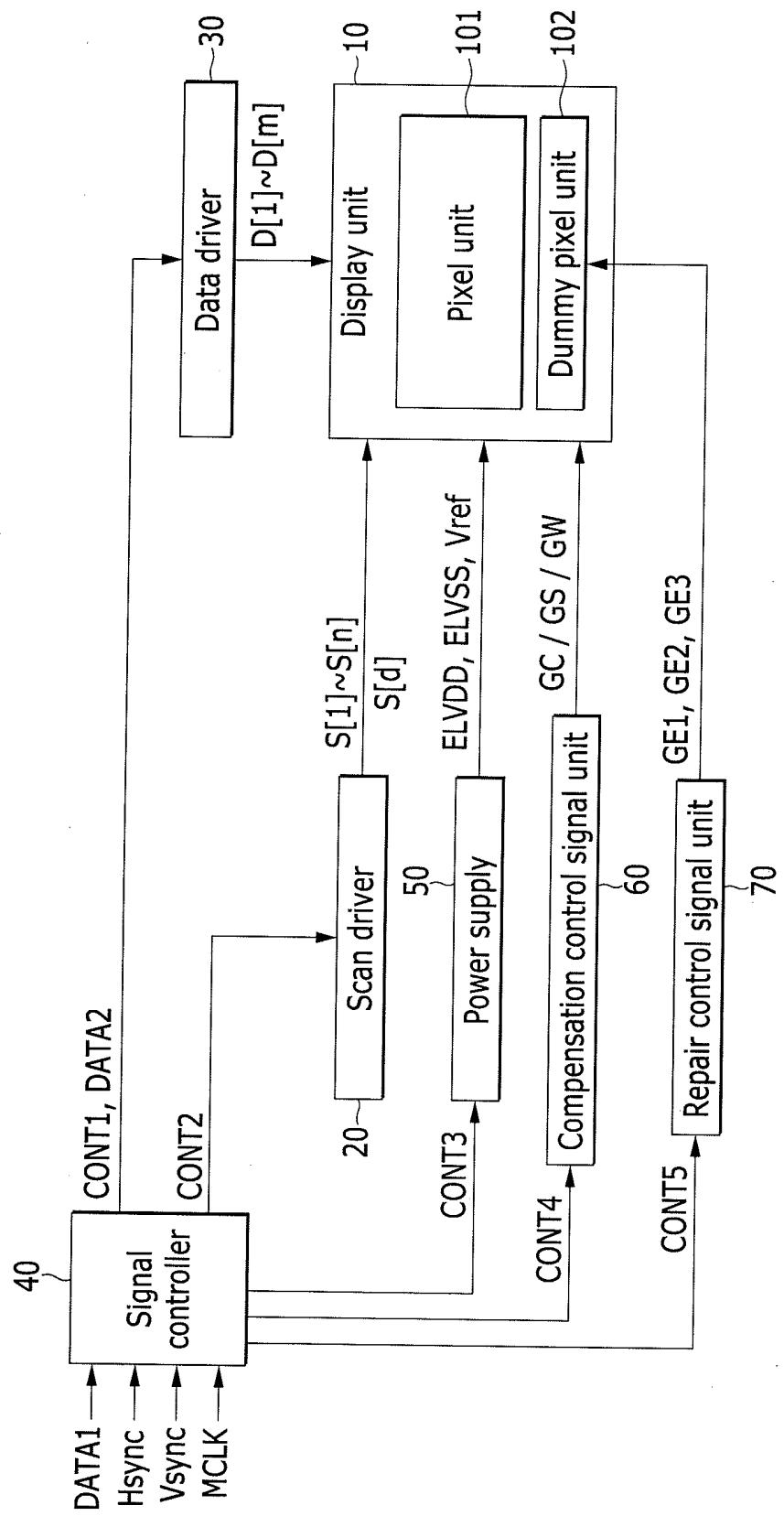

[0043] FIG. 1 is a block diagram of a display device according to an exemplary embodiment.

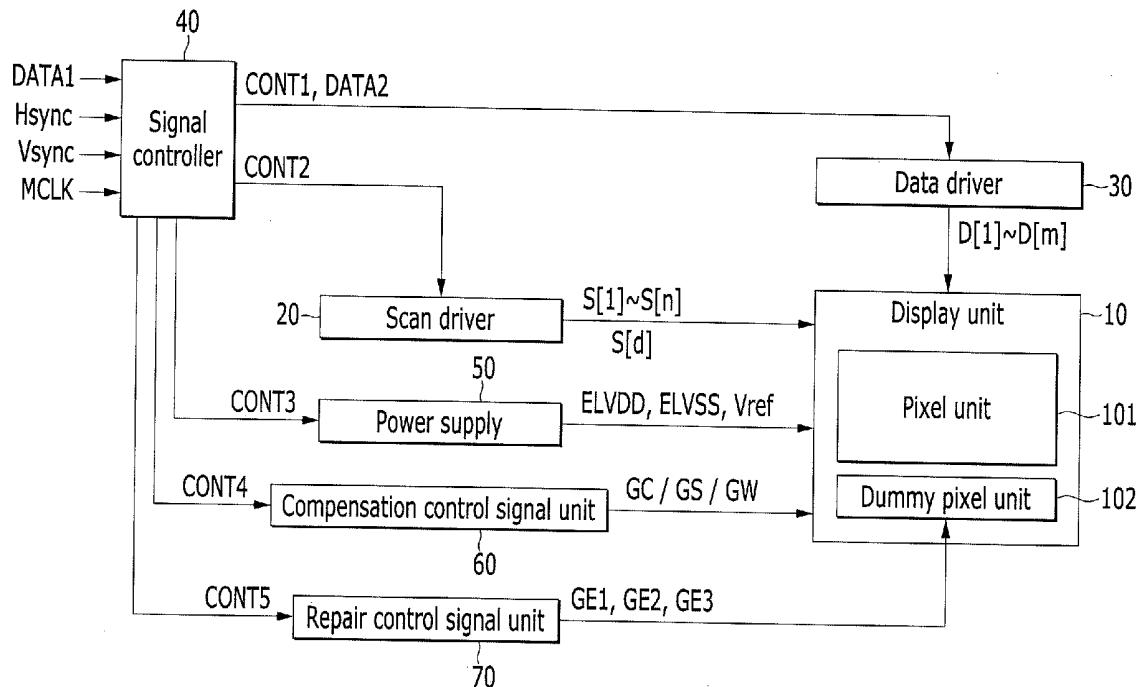

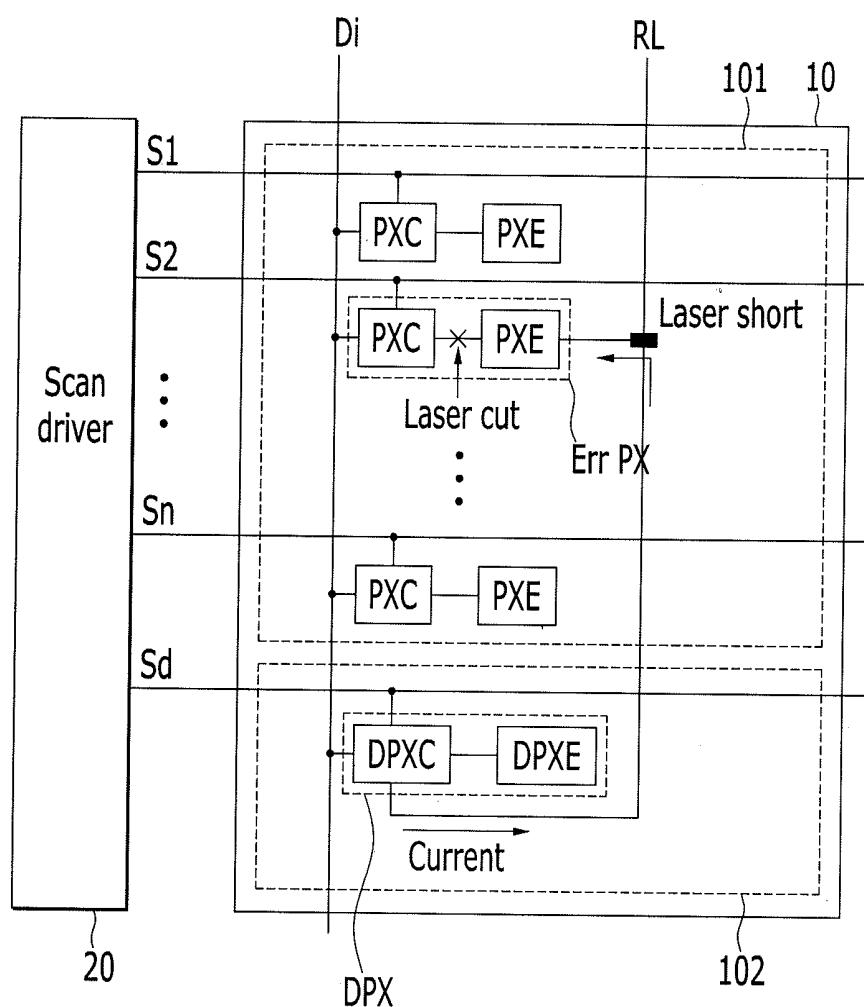

[0044] FIG. 2 shows a partial connection structure of a pixel in the display unit of FIG. 1 and a method for recovering the functionality of a defective pixel.

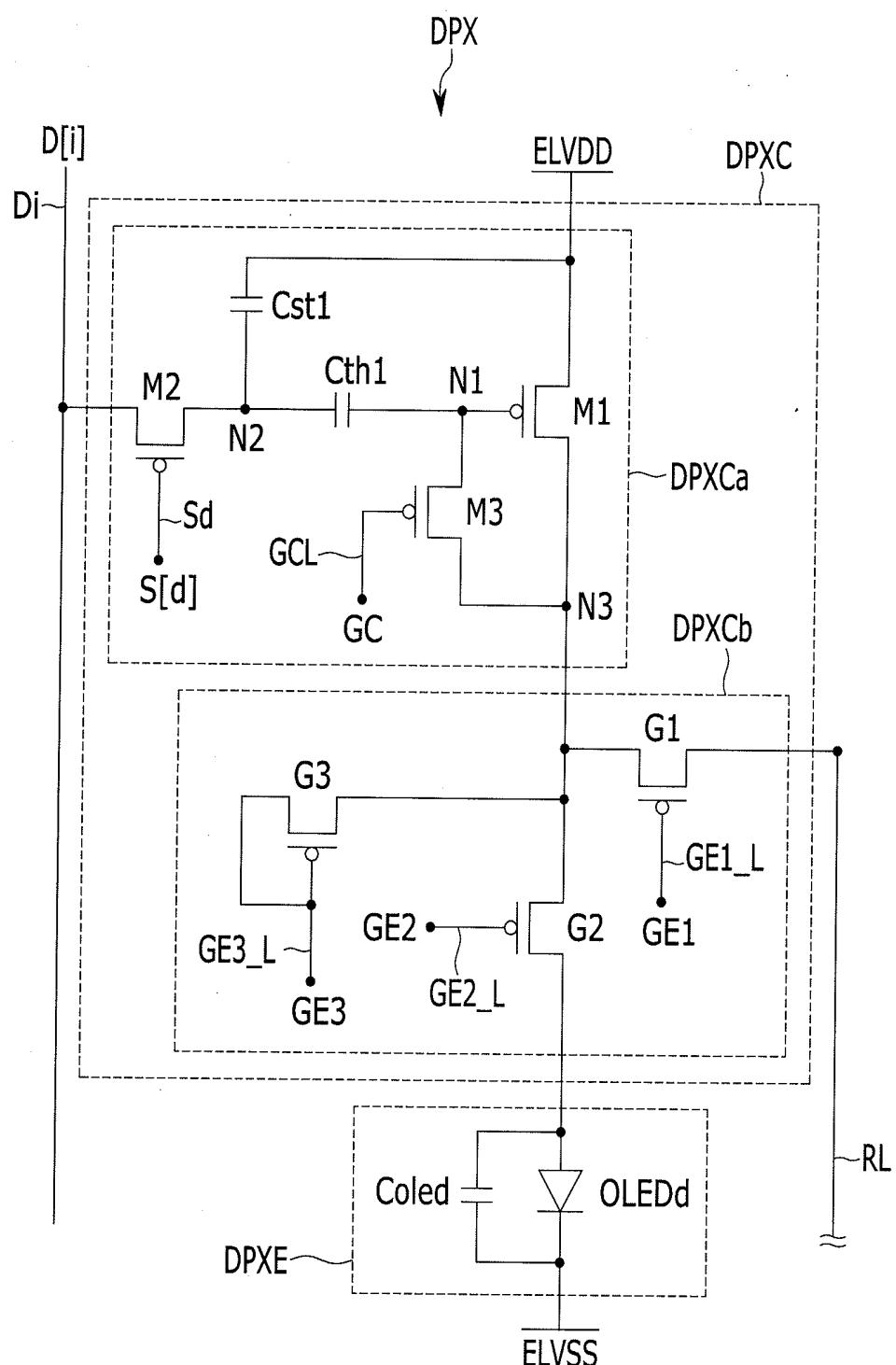

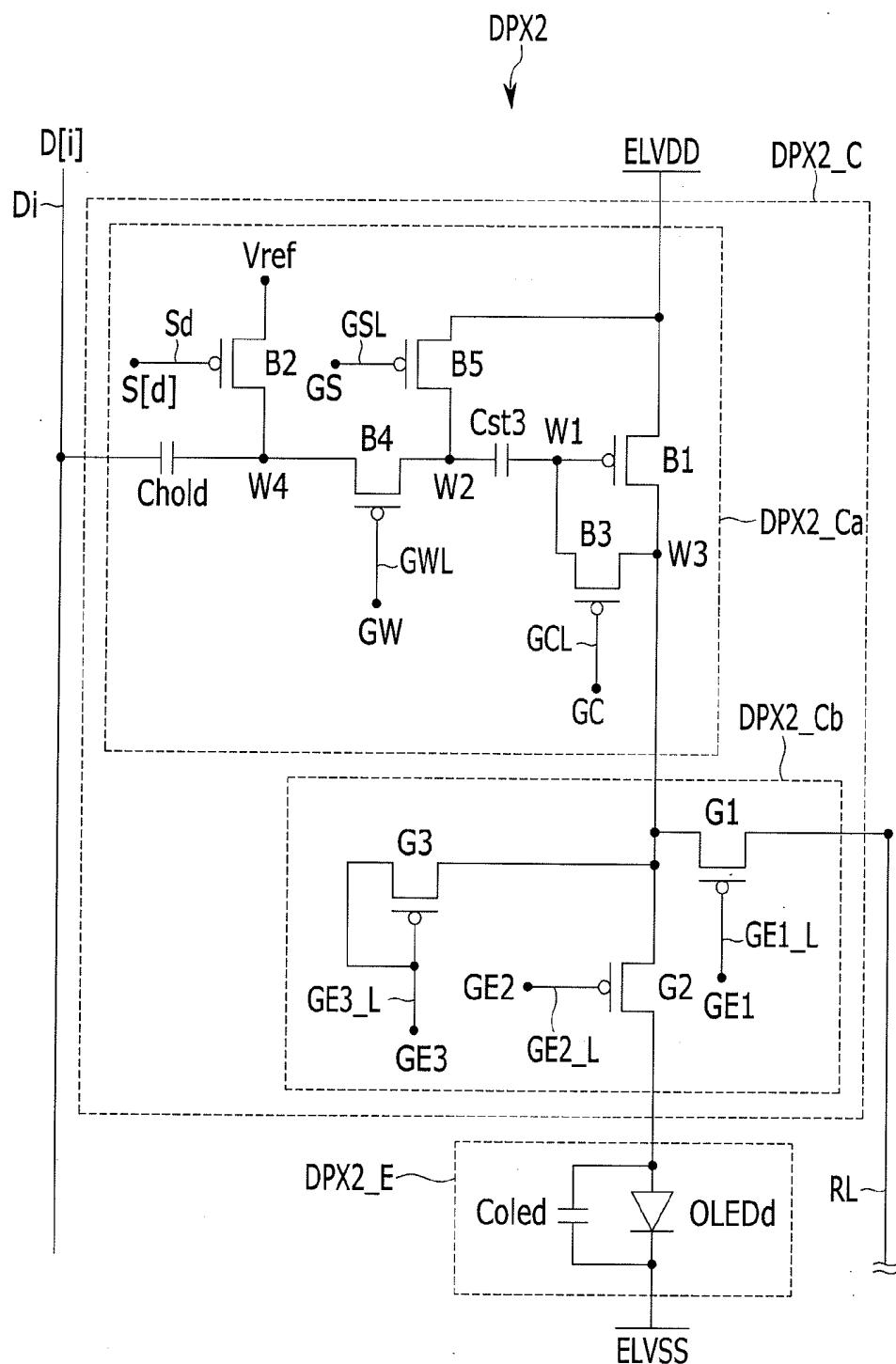

[0045] FIG. 3 is a circuit diagram of the structure of a dummy pixel of the display device according to an exemplary embodiment.

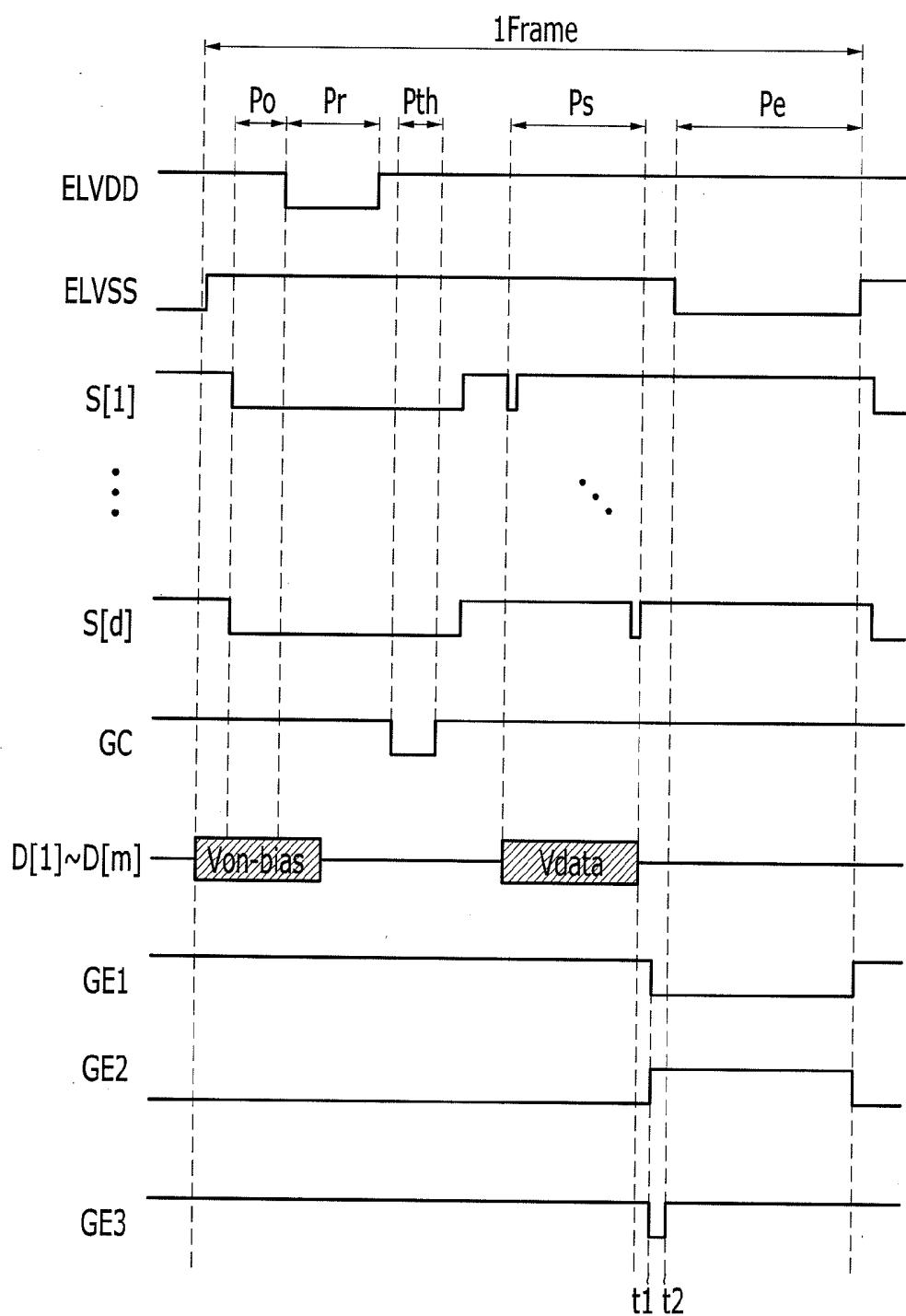

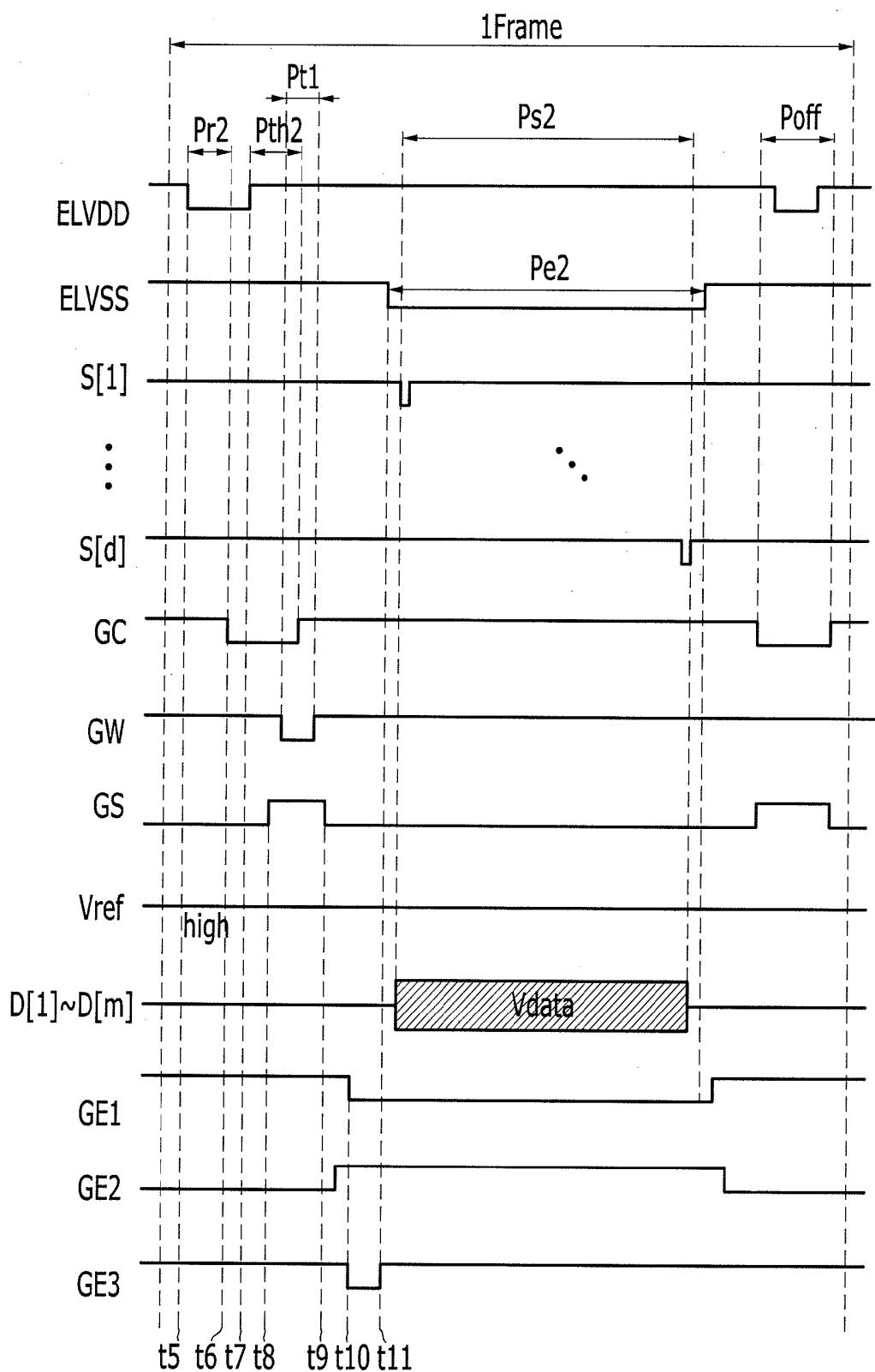

[0046] FIG. 4 is a timing diagram provided for describing a driving method of the display and a method for driving the dummy pixel according to the exemplary embodiment of FIG. 3.

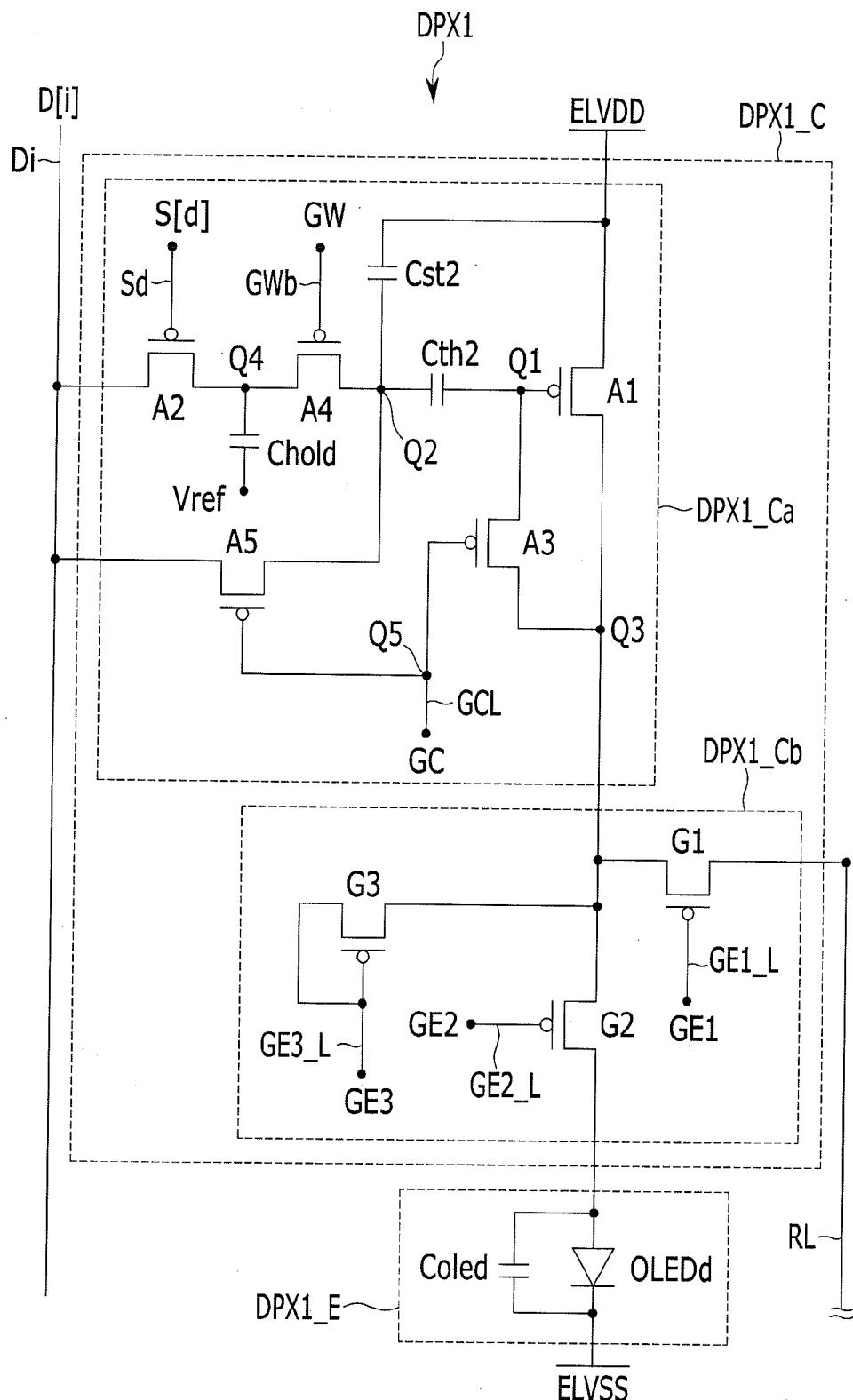

[0047] FIG. 5 is a circuit diagram of the structure of a dummy pixel of a display device according to another exemplary embodiment.

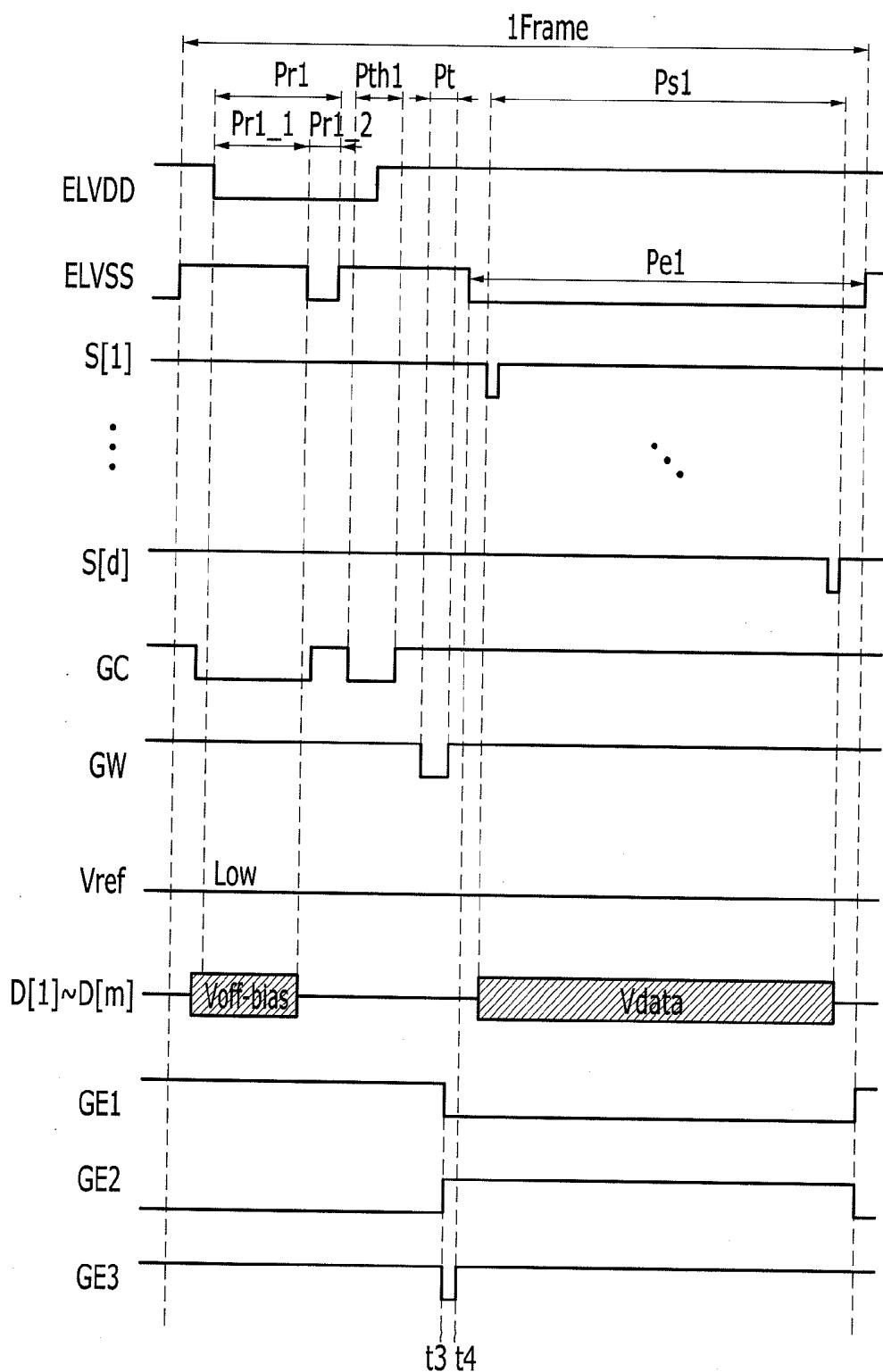

[0048] FIG. 6 is a timing diagram provided for describing a method for driving the display device and a method for driving the dummy pixel according to the exemplary embodiment of FIG. 5.

[0049] FIG. 7 is a circuit diagram of the structure of a dummy pixel according to another exemplary embodiment.

[0050] FIG. 8 is a timing diagram provided for describing a method for driving the display device and a method for driving the dummy pixel according to the exemplary embodiment of FIG. 7.

#### DETAILED DESCRIPTION OF CERTAIN INVENTIVE EMBODIMENTS

[0051] The described technology will be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the described technology are shown. As those skilled in the art would realize, the described embodiments may be modified in various different ways, all without departing from the spirit or scope of the described technology.

[0052] Further, in exemplary embodiments, since like reference numerals are used to designate like elements having the same configuration, a first exemplary embodiment is representatively described, and in other exemplary embodiments, only those configurations different from the first exemplary embodiment will be described.

[0053] Accordingly, the drawings and the description are to be regarded as illustrative in nature and not restrictive. Like reference numerals designate like elements throughout the specification.

[0054] Throughout the specification and the accompanying claims, when it is described that an element is "coupled" to another element, the element may be "directly coupled" to the other element or "coupled" to the other element through a third element. Throughout the specification, "connected" and "coupled" respectively include "electrically connected" and "electrically coupled." In addition, unless explicitly described to the contrary, the word "comprise" and variations such as "comprises" or "comprising" will be understood to imply the inclusion of the stated elements but not the exclusion of any other elements.

[0055] FIG. 1 is a block diagram of a display device according to an exemplary embodiment.

[0056] Referring to FIG. 1, a display device includes a display unit 10, a scan driver 20, a data driver 30, a signal controller 40, a power supply 50, a compensation control signal unit 60, and a repair control signal unit 70.

[0057] The display device may include at least one of each of the compensation control signal unit 60 and the repair control signal unit 70 according to the configuration of a plurality of pixels included in the display unit 10 and the driving method thereof.

[0058] The display unit 10 is a display area including a plurality of pixels arranged substantially in a matrix format.

[0059] In further detail, the display unit 10 according to the present exemplary embodiment includes a pixel unit 101 which is a display area which may display an image and a dummy pixel unit 102 which is a dummy area that recovers and compensates for defective pixels of the pixel unit 101.

[0060] That is, the pixel unit 101 of the display unit 10 is formed of a plurality of pixels which display an image corresponding to a data signal according to an external image signal. In addition, the dummy pixel unit 102 of the display unit 10 is formed of a plurality of dummy pixels that assist a defective pixel in the plurality of pixels included in the pixel unit 101 to be driven as a normal pixel by repairing the defective pixel.

[0061] In the pixel unit 101 of the display unit 10, a plurality of scan lines extended substantially in a row direction, substantially parallel with each other, a plurality of data lines

extended substantially in a column direction, substantially parallel with each other, and a plurality of power supply lines which supply a plurality of power voltages are respectively connected to the plurality of pixels.

[0062] In addition, according to an exemplary embodiment, the dummy pixel unit 102 may be extended in a row direction or a column direction on one side of the pixel unit 101. In the exemplary embodiment of FIG. 1, the dummy pixel unit 102 may include a dummy pixel additionally formed on one side of each pixel column of the plurality of pixels.

[0063] However, the described technology is not restricted to the exemplary embodiment described above. The dummy pixel unit may be iteratively extended in a row direction or a column direction for every several tens or several hundreds of pixel lines in the pixel unit.

[0064] In addition, although not shown in FIG. 1, each of the plurality of dummy pixels included in the dummy pixel unit 102 may be connected to a repair line that is extended to an anode of each of the plurality of pixels in the pixel unit 101 to repair a defective pixel among the plurality of pixels included in the pixel unit 101. The alignment of the dummy pixels and the repair line and a method for repairing a defective pixel will be described in further detail with reference to FIG. 2.

[0065] Further, each of the plurality of pixels included in the pixel unit 101 and each of the dummy pixels included in the dummy pixel unit 102 of the display unit 10 are connected to a plurality of first to third control lines GCL, GWL, and GSL (not shown) according to the configuration and the driving method thereof.

[0066] In addition, each of the dummy pixels of the dummy pixel unit 102 is connected to a plurality of first to third relay control lines GE1\_L, GE2\_L, and GE3\_L (not shown).

[0067] The scan driver 20 is connected to a plurality of scan lines connected to each line of the plurality of pixels and the dummy pixels of the display unit 10, and generates and transmits a plurality of scan signals S[1] to S[n] respectively corresponding to the plurality of scan lines according to a scan driving control signal CONT2.

[0068] Among the plurality of scan signals, scan signals S[1]-S[n] are transmitted to the respective pixel lines of the plurality of pixels in the pixel unit 101, and a scan signal S[d] is transmitted to the plurality of dummy pixels of the dummy pixel unit 102. Although the scan signal S[d] transmitted to the dummy pixel unit 102 is described as being sequentially transmitted after the sequential transmission of the plurality of scan signals S[1] to S[n] to the pixel unit 101 in FIG. 1, it is not restricted thereto. A scan signal for a dummy pixel may be connected to a scan line connected to the dummy pixel unit depending on the configuration and alignment of the dummy pixel unit 102.

[0069] The scan driver 20 sequentially applies the scan signals S[1] to S[n] and S[d] having a pulse voltage with a gate-on level of a transistor formed in a pixel to the plurality of scan lines.

[0070] The data driver 30 is connected to a plurality of data lines connected to each of the plurality of pixels and each of the dummy pixels of the display unit 10 for each column, and samples and holds an externally input image signal DATA 1 according to a data driving control signal CONT1, and transmits data voltages D[1] to D[m] that depends on a plurality of image-processed image data signals DATA2 respectively the plurality of data lines.

[0071] The data driver 30 applies data voltages D[1] to D[m] having a predetermined range to the plurality of data lines corresponding to the scan signals S[1] to S[n] having the gate-on pulse voltage.

[0072] The signal controller 40 receives the externally input image signal DATA1 and a synchronization signal. The image signal DATA1 includes luminance information for the plurality of pixels. Luminance may be classified into a predetermined number of gray levels, for example, 1024 ( $=2^{10}$ ), 256 ( $=2^8$ ), or 64 ( $=2^6$ ) gray levels. The synchronization signal includes a horizontal synchronization signal Hsync, a vertical synchronization signal Vsync, and a main clock signal MCLK.

[0073] The signal controller 40 generates a plurality of driving control signals CONT1 to CONT5 and the image data signal DATA2 according to the horizontal synchronization signal Hsync, the vertical synchronization signal Vsync, and the main clock signal MCLK.

[0074] The signal controller 40 divides the image signal DATA1 per frame unit according to the vertical synchronization signal Vsync and divides the image signal DATA1 per scan line unit to generate the image data signal DATA2.

[0075] The signal controller 40 transmits the image data signal DATA2 and the data driving control signal CONT1 to the data driver 30.

[0076] In addition, the signal controller 40 transmits the scan driving control signal CONT2 to the scan driver 20 so that the scan driver 20 may sequentially transmit the plurality of scan signals S[1] to S[n] having the gate-on pulse voltage.

[0077] In addition, the signal controller 40 may generate a power supply control signal CONT3 transmitted to the power supply 50, a compensation driving control signal CONT4 transmitted to the compensation control signal unit 60, and a repair driving control signal CONT5 transmitted to the repair control signal unit 70.

[0078] According to the driving method of the display device and the configuration of the pixels, the power supply control signal CONT3, the compensation driving control signal CONT4, and the repair driving control signal CONT5 may be formed as a plurality of driving control signals respectively having different control functions.

[0079] In further detail, the power supply control signal CONT3 may include a plurality of different power supply control signals that control a voltage level and timing for each of a first power source voltage ELVDD, a second power source voltage ELVSS, and a reference voltage Vref that are supplied from the power supply 50.

[0080] In addition, the compensation driving control signal CONT4 may include a plurality of different compensation driving control signals that control a pulse voltage level and timing for each of a first control signal GC, a second control signal GW, and a third control signal GS that are supplied from the compensation control signal unit 60.

[0081] In addition, the repair driving control signal CONT5 may include a plurality of different repair driving control signals that control a pulse voltage level and timing for each of a first repair control signal GE1, a second repair control signal GE2, and a third repair control signal GE3 that are generated from the repair control signal unit 70.

[0082] Meanwhile, the power supply 50 determines the level of each of the first power source voltage ELVDD, the second power source voltage ELVSS, and the reference voltage Vref according to the power supply control signal

CONT3 and then supplies the determined voltages to the power supply lines connected to the plurality of pixels.

[0083] The first power source voltage ELVDD and the second power source voltage ELVSS supply a driving current to the pixels. According to the driving type of the display device, the power supply 50 controls the timing of the application of the second power voltage ELVDD as a low level voltage according to a predetermined value of the maximum luminance of the pixels to control the light emission period during which the plurality of pixels substantially simultaneously emit light. The power supply 50 controls the timing of the application of the first power source voltage ELVDD as a low level voltage to control the reset of and a threshold voltage compensation period of the plurality of pixels. In addition, the power supply 50 may supply the reference voltage Vref to an additional power supply line connected to the plurality of pixels.

[0084] The compensation control signal unit 60 determines a pulse voltage level of at least one of the first control signal GC, the second control signal GW, and the third control signal GS according to the compensation driving control signal CONT4 and applies the signals having the determined pulse voltage level to the corresponding control lines connected to the display unit.

[0085] In further detail, according to the implementation type, the compensation control signal unit 60 generates the first control signal GC and transmits the same to a first control line (not shown) according to the compensation driving control signal CONT4. In addition, according to the configuration of the pixels and the driving method of the display device, the compensation control signal unit 60 may additionally generate the second control signal GW and transmit the same to a second control line (not shown), or may generate the third control signal GS and transmit the same to a third control line (not shown).

[0086] Here, the first control signal GC may be a control signal for compensation of a threshold voltage of a driving transistor of the pixels, and the second control signal GW may be a control signal for relaying a data voltage that depends on the corresponding image data signal applied to the previous frame to a predetermined node in the pixels for light emission. Further, the third control signal GS may be a control signal for maintaining a predetermined node voltage in the pixels for a predetermined time period.

[0087] The repair control signal unit 70 determines the pulse voltage level of the first repair control signal GE1, the second repair control signal GE2 and the third repair control signal GE3 according to the repair driving control signal CONT5 and applies the signals having the determined pulse voltage levels to the corresponding repair control lines connected to the dummy pixel unit 102 of the display unit.

[0088] In further detail, the repair control signal unit 70 generates the first repair control signal GE1 according to the repair driving control signal CONT5 and transmits the same to a first repair control line GE1\_L (not shown). In addition, the repair control signal unit 70 generates the second repair control signal GE2 and transmits the same to a second repair control line GE2\_L (not shown), and generates the third repair control signal GE3 and transmits the same to a third repair control line GE3\_L (not shown).

[0089] FIG. 2 schematically shows a part of the pixel connection structure of the display unit 10 of FIG. 1 and a method for repairing a defective pixel according to an exemplary embodiment.

[0090] In further detail, FIG. 2 illustrates pixels and dummy pixels arranged in the i-th column of the plurality of pixels and the plurality of dummy pixels respectively included in the pixel unit 101 and the dummy pixel unit 102 of the display unit 10 in FIG. 1.

[0091] The pixels and a dummy pixel DPX arranged in the i-th column are connected with the corresponding scan lines S1 to Sn and Sd connected to the scan driver 20 for each line. In addition, a data line Di corresponding to the i-th column is connected to the pixels and the dummy pixel DPX.

[0092] The pixels and the dummy pixel DPX are respectively formed of driving circuits which generate driving currents according to data signals and transmit the driving currents to light emission portions which emit light with luminance corresponding to the driving current. That is, each of the plurality of pixels included in the pixel unit 101 of the display unit 10 is formed of a driving circuit PXC and a light emission portion PXE. In addition, according to the present exemplary embodiment, each of the plurality of dummy pixels DPX included in the dummy pixel unit 102 of the display unit 10 is also formed of a driving circuit DPXC and a light emission portion DPXE.

[0093] In FIG. 2, each of the plurality of pixels included in the pixel unit 101 is connected to a corresponding scan line that corresponds to the driving circuit PXC and the i-th data line such that operation of the pixel is controlled by the corresponding scan signal and the driving circuit PXC generates a driving current according to the transmitted data signal. In addition, the driving current generated from the driving circuit PXC of the pixel is transmitted to the light emission portion PXE and thus light is emitted with a corresponding luminance such that an image is displayed.

[0094] The dummy pixel of the dummy pixel unit 102 of FIG. 2 is also connected with the scan line Sd for the dummy pixel corresponding to the driving circuit DPXC and the i-th data line. In addition, according to the present exemplary embodiment, the dummy pixel includes a light emission portion DPXE connected to the driving circuit DPXC.

[0095] Light emitted from the light emission portion DPXE of the dummy pixel is controlled according to the first to third repair control signals transmitted from the repair control signal unit 70.

[0096] In the exemplary embodiment of FIG. 2, the dummy pixels DPX are arranged in the lowest end of the column of pixels, and the dummy pixel DPX and each of the plurality of pixels arranged in the upper portion of the column may be connected to each other through a repair line RL disposed along the column direction. In further detail, the repair line RL is extended to the driving circuit of the dummy pixel from the anodes of each of the plurality of pixels of the pixel unit 101. The driving circuit DPXC of the dummy pixel and the repair line RL may be connected and an anode of a light emission portion PXE of a pixel (i.e., a defective pixel) and the repair line RL may be connected by a laser short.

[0097] Thus, when a driving circuit of a pixel among the plurality of pixels is defective, the anode of a light emission portion of the pixel and the repair line are short-circuited by a laser, and a driving circuit DPXC of a dummy pixel formed in the corresponding column of the defective pixel and the repair line are short-circuited by a laser. Then, a driving current that depends on an image data signal corresponding to the defective pixel is transmitted to the light emission portion of the defective pixel from the driving circuit of the dummy pixel

DPX through the repair line. Accordingly, the defective pixel is repaired to functions as a normal pixel and thus generates light with normal luminance.

[0098] In this case, the connection between the driving circuit PXC and the light emission portion PXE of the defective pixel should be cut by the laser.

[0099] In the exemplary embodiment of FIG. 2, when the second pixel of the i-th column is determined to be a defective pixel ErrPX and thus the driving circuit PXC thereof cannot be driven normally, the connection between a driving circuit PXC and a light emission portion PXE of the defective pixel ErrPX is cut by a laser and the light emission portion PXE of the defective pixel ErrPX and the repair line RL are connected using a laser short. Since the repair line RL is connected to the driving circuit DPXC of the dummy pixel DPX corresponding to the defective pixel ErrPX, a driving current is transmitted to the light emission portion PXE of the defective pixel ErrPX by the driving circuit DPXC of the dummy pixel DPX so that light may be emitted normally.

[0100] FIG. 3 is a circuit diagram of a dummy pixel structure of a display device according to an exemplary embodiment.

[0101] A dummy pixel DPX of the display device according to the exemplary embodiment of FIG. 3 is included in the dummy pixel unit 102 of FIG. 2, and is formed of the driving circuit DPXC of the dummy pixel and the light emission portion DPXE of the dummy pixel.

[0102] The driving circuit DPXC of the dummy pixel is connected with the repair line RL by a laser short when a defective pixel is detected in the pixel unit 101 of the display unit and thus the driving circuit DPXC is electrically connected with the light emission portion of the defective pixel.

[0103] In addition, the driving circuit DPXC of the dummy pixel may be formed of a first driving portion, that is, a light emission driver DPXCa, and a second driving portion, that is, a repair driver DPXCb.

[0104] The light emission driver DPXCa is a circuit that activates the corresponding dummy pixel DPX to generate and transmit a driving current for a data voltage for light emission.

[0105] In addition, the repair driver DPXCb is a compensation circuit that compensates for a failure in the defective pixel by being connected with the repair line RL using a laser short in the corresponding dummy pixel DPX when a defective pixel is generated in the pixel unit 101.

[0106] In the display device according to the present exemplary embodiment, the structure of each of the plurality of pixels included in the pixel unit 101 is not illustrated, however, each of the plurality of pixels may have the same structure as that of the dummy pixel DPX, excluding the repair driver DPXCb of the dummy pixel DPX. That is, each of the plurality of pixels that form the pixel unit to display an image according to an image signal has a structure in which the light emission driver DPXCa and the light emission portion DPXE of the dummy pixel DPX are connected.

[0107] In further detail, referring to FIG. 3, the light emission driver DPXCa of the dummy pixel includes a driving transistor M1, a switching transistor M2, a compensation transistor M3, a storage capacitor Cst1, and a compensation capacitor Cth1. The light emission driver DPXCa of FIG. 3 is commonly used for the pixels included in the pixel unit, and therefore the connections and functions of the circuits included in each of the light emission drivers of the pixels are the same as the circuit included in the light emission drivers of

the dummy pixel. [0106] The driving transistor M1 includes a gate electrode connected to a first node N1, a first electrode connected to the first power source voltage ELVDD, and a second electrode connected to a third node N3.

[0108] The driving transistor M1 generates a driving current corresponding to a data voltage that depends on an image data signal transmitted to the first node N1 and transmits the driving current to the organic light-emitting diode of the light emission portion.

[0109] The switching transistor M2 includes a gate electrode connected to the corresponding scan line Sd among the plurality of scan lines, a first electrode connected to the corresponding data line Di among the plurality of data lines, and a second electrode connected to the second node N2.

[0110] The switching transistor M2 is turned on by a scan signal S[d] having a pulse voltage of a gate-on level transmitted through the scan line Sd and transmits a data voltage D[i] that depends on the image data signal transmitted through the data line Di to the second node N2.

[0111] The compensation transistor M3 includes a gate electrode connected to the first control line GCL, a first electrode connected to the first node N1, and a second electrode connected to the third node N3.

[0112] The compensation transistor M3 is turned on by the first control signal GC having a pulse voltage of a gate-on level transmitted through the first control line GCL and diode-connects the gate electrode and the second electrode of the driving transistor M1. Thus, in the equation for calculating the amount of driving current that depends on the data voltage applied to a gate electrode terminal of the driving transistor M1, the threshold voltage of the driving transistor is removed to eliminate and compensate for a threshold voltage deviation of the driving transistors of the pixels included in the display unit.

[0113] The storage capacitor Cst1 includes a first electrode connected to the first power source voltage ELVDD and a second electrode connected to the second node N2. Since the storage capacitor Cst1 stores a voltage value corresponding to a voltage difference between lateral ends of the storage capacitor Cst1, the storage capacitor Cst1 maintains and stores the data voltage applied to the second node N2.

[0114] The compensation capacitor Cth1 includes a first electrode connected to the first node N1 and a second electrode connected to the second node N2. The compensation capacitor Cth1 maintains a voltage difference between lateral ends thereof, and therefore the compensation capacitor Cth1 maintains a voltage value corresponding to the threshold voltage of the driving transistor applied to the first node N1 during a compensation period of the driving transistor.

[0115] Meanwhile, the light emission portion DPXE of the dummy pixel includes an organic light-emitting diode OLEDd connected to the repair driver DPXCb. Similarly, each of the plurality of pixels included in the pixel unit 101 includes an organic light-emitting diode OLED.

[0116] The organic light-emitting diode OLEDd includes an anode connected to the repair driver DPXCb and a cathode connected to the second power source voltage ELVSS.

[0117] The organic light-emitting diode includes an organic emission layer which emits light corresponding to a primary color. An example of a primary color may include red, green, or blue, and a desired color may be displayed as a spatial or temporal sum of primary colors.

[0118] The organic light-emitting diode OLED emits light with luminance that corresponds to the driving current which

depends on the data signal transmitted from the driving transistor M1 to thereby display an image.

[0119] Further, the display device according to the exemplary embodiment includes a dummy pixel that further includes a repair driver DPXCb, and the repair driver DPXCb includes a first repair transistor G1, a second repair transistor G2, and a third repair transistor G3.

[0120] In the display device, the repair driver DPXCb is not included in each of the plurality of pixels of the pixel unit 101.

[0121] The first repair transistor G1 includes a gate electrode connected to the first repair control line GE1\_L, a first electrode connected to the third node N3, and a second electrode connected to the repair line RL. The first repair transistor G1 is turned on in responding to a pulse voltage of a gate-on level of the first repair control signal GE1 transmitted through the first repair control line GE1\_L. Then, the first repair transistor G1 transmits a driving current that depends on the data voltage transmitted from the driving transistor M1 through the repair line RL. The repair line RL is electrically connected to a pixel which has had a driving failure from among the plurality of pixels included in the pixel unit 101, and an electrical connection may be established by the laser short. Thus, the driving current that depends on the data voltage transmitted through the first repair transistor G1 of the dummy pixel DPX is transmitted to an organic light-emitting diode of the pixel having the driving failure through the repair line RL, and the organic light-emitting diode emits light with a corresponding luminance.

[0122] Then, although a pixel has experienced a driving failure, the organic light-emitting diode of the defective pixel may emit light normally, thereby preventing luminance deterioration of the entire display unit.

[0123] The first repair transistor G1 maintains the turned-on state only during the light emission period of the display unit, and the driving current is transmitted to the repair line RL during this period so that the organic light-emitting diode of the defective pixel in the pixel unit can emit light. This will be described later in further detail in the description of driving timing.

[0124] The second repair transistor G2 includes a gate electrode connected to the second repair control line GE2\_L, a first electrode connected to the third node N3, and a second electrode connected to the anode of the organic light-emitting diode OLEDd of the dummy pixel. The second repair transistor G2 is turned-on in response to a pulse voltage of a gate-on level of the second repair control signal GE2 transmitted through the second repair control line GE2\_L. Then, the second repair transistor G2 substantially simultaneously performs initialization (or, reset) and compensation of a threshold voltage of the driving transistors for each of the plurality of pixels included in the pixel unit by using an organic light-emitting diode capacitor Coled included in the organic light-emitting diode OLEDd of the dummy pixel connected to the second electrode of the second repair transistor G2.

[0125] When a defective pixel has experienced a driving failure in the plurality of pixels included in the pixel unit, the driving current should be transmitted to the defective pixel using the repair line RL during the light emission period, and therefore the pulse voltage of the repair control signal GE2 is at a gate-off level and the second repair transistor G2 maintains a turned-off state.

[0126] The third repair transistor G3 includes a gate electrode connected to the third repair control line GE3\_L, a first

electrode connected to the third node N3, and a second electrode connected to the gate electrode terminal of the third repair transistor G3. That is, the third repair transistor G3 has a diode-connection structure so as to have the same characteristics as the organic light-emitting diode. The third repair transistor G3 is turned-on in response to a pulse voltage of a gate-on level of the third repair control signal GE3 transmitted through the third repair control line GE3\_L. Then, a driving current which depends on the data voltage flowing in the driving transistor M1 connected to the third node N3 flows through the turned-on third repair transistor G3 with the same characteristics as the organic light-emitting diode. Thus, the voltage of an organic light-emitting diode of the previous frame, applied to the repair line RL can be reset to a voltage of an organic light-emitting diode that is going to emit light.

[0127] That is, for such a reset, the third repair control signal GE3 is transmitted at a gate-on voltage level at the same time as the first repair transistor G1 is turned-on, that is, during a predetermined period at the initial stage of the light emission period.

[0128] The transistors forming the dummy pixel DPX of FIG. 3 may be PMOS transistors, but are not limited thereto. The transistors may alternatively be formed as an NMOS transistors.

[0129] A driving method and timing of the dummy pixel PDX and the plurality of pixels included in the pixel unit 101 are shown in FIG. 4. The timing diagram of FIG. 4 will be described in connection with the dummy pixel structure of FIG. 3, and therefore the voltage level that turns on the PMOS transistors of FIG. 3 is a low voltage level.

[0130] The circuit configuration of a general pixel is the same as that of the dummy pixel excluding the repair driver DPXCb of the dummy pixel, and therefore the operation for each pixel is the same as that of the dummy pixel.

[0131] In the timing diagram of FIG. 4, the dummy pixel 102 is provided in a lower end of the pixel unit 101 as in FIG. 1. Therefore, timing diagrams illustrated may apply to various exemplary embodiments.

[0132] Referring to FIG. 4, one frame period during which one image is displayed in the display unit 10 includes an on-bias period Po for improving a response waveform of a plurality of pixels, a reset period Pr for resetting the driving voltage of the organic light-emitting diode of each pixel, a compensation period Pth for compensating for a threshold voltage of the driving transistor of each pixel, a scan period Ps for transmitting a data voltage to each pixel, and a light emission period Pe for substantially simultaneous light emission of the plurality of pixels corresponding to the data voltage applied to the gate voltage of the driving transistors.

[0133] First, during the on-bias period Po, the first power source voltage ELVDD and the second power source voltage ELVSS are provided as high level voltages. In addition, the plurality of scan signals S[1] to S[d] transmitted to the plurality of pixels and the plurality of dummy pixels of the entire display unit are applied with low level voltages. Here, the scan signals S[1] to S[n] among the plurality of scan signals are scan signals respectively transmitted to each pixel line of the plurality of pixels that correspond to the pixel unit, and the scan signal S[d] is a scan signal transmitted to the plurality of dummy pixels that correspond to the dummy pixel unit provided in the lower end of the pixel unit. The scan signal S[d] is a scan signal transmitted to the dummy pixels formed of at least one line, like the dummy pixel unit of FIG. 1.

[0134] In addition, during the on-bias period Po, the first control signal GC is applied as a high level voltage, and the plurality of data signals D[1] to D[m] transmitted to the display unit are applied as a predetermined on-bias voltage Von-bias.

[0135] During this period, the first repair control signal GE1 and the third repair control signal GE3 are applied as high level voltages and the second repair control signal GE2 is applied as a low level voltage in the plurality of dummy pixels.

[0136] During the on-bias period Po, the plurality of pixels and the plurality of dummy pixels of the entire display unit are substantially simultaneously turned on according to the plurality of scan signals S[1] to S[d]. Then, a voltage according to the corresponding data signal among the plurality of data signals D[1] to D[m] is applied to a gate electrode terminal of the driving transistor M1, that is, the first node N1 in the circuit diagram of FIG. 3 through the data line. During this period, the plurality of data signals D[1] to D[m] are applied as the predetermined bias voltage Von-bias, and therefore, the gate electrodes of the driving transistors M1 of the entire pixels of the display unit are applied with the on-bias voltage Von-bias.

[0137] Since the gate electrodes of the driving transistors M1 of all the pixels are applied with a specific voltage (i.e., the on-bias voltage Von-bias) in advance, the response waveform of the pixels can be improved. According to the implementation type, the on-bias period Po may be omitted.

[0138] While the respective pixels of the display unit are in the turned-on state, the first power source voltage ELVDD is applied as a low level voltage during the reset period Pr. In the reset period Pr, the second power source voltage ELVSS is applied as a high level voltage. Thus, no current flows toward the organic light-emitting diode OLEDd from the driving transistor M1, but a voltage of the third node N3 passes through the turned-on driving transistor M1 and thus reaches the low-level voltage of the first power source voltage ELVDD. The third node N3 is a drain electrode terminal of the driving transistor M1, and the path of the driving current according to the image data signal is formed to the organic light-emitting diode through the third node N3. Therefore, the level of the driving current that depends on the image data signal transmitted in the previous frame is reset by the low level voltage of the first power source voltage ELVDD.

[0139] In the case of the plurality of dummy pixels, only the second repair transistor G2 is turned on at this time due to the second repair control signal GE2 applied as low level signal, and therefore, the drain electrode terminal (i.e., third node electrode) of the driving transistor of the dummy pixels is reset by the low-level first power source voltage ELVDD, just like the reset process for the plurality of pixels.

[0140] Next, during the compensation period Pth, the first power source voltage and the second power source voltage are applied as high level voltages while each of the plurality of pixels of the display unit is turned on by a scan signal. In this case, the first control signal GC is applied as a low-level gate-on voltage. The compensation transistor M3 is turned on with the first control signal GC. While the compensation transistor M3 is turned on, the driving transistor M1 is diode-connected and the threshold voltage of the driving transistor M1 is transmitted to the first node N1. Accordingly, the threshold voltage of the driving transistor M1 is stored in the compensation capacitor Cth1. The threshold voltage of the driving transistor M1 is thus removed from the calculation of

the amount of driving current according to the input image data signal, and therefore the threshold voltage characteristic deviation of the driving transistor in each pixel can be eliminated. That is, the threshold voltage of the driving transistor of each pixel is compensated for during the compensation period Pth.

[0141] Thus, the display device can display an image with uniform luminance without regard to a deviation of the threshold voltage caused due to the characteristics of the driving transistor.

[0142] After the termination of the compensation period Pth, the plurality of scan signals S[1] to S[d] are increased to a high level. In addition, the first control signal GC is also increased to a high level.

[0143] During the scan period Ps, the plurality of scan signals S[1] to S[d] are sequentially transmitted to the plurality of pixels of the corresponding pixel lines with a low-level pulse voltage for each pixel line. The scan signal S[d] is also transmitted as the low-level pulse voltage to each of the plurality of dummy pixels at the lowest end of the dummy pixel line.

[0144] Then, the switching transistor M2 of FIG. 3 is turned on, and a data voltage Vdata that depends on the corresponding data signal among the plurality of data signals D[1] to D[m] is transmitted to the first electrode of the switching transistor M2.

[0145] The data voltage Vdata that depends on the data signal is transmitted to the second node N2 of each pixel and then stored in the storage capacitor Cst1.

[0146] During the on-bias period Po, the reset period Pr, the compensation period Pth, and the scan period Ps, the second power source voltage ELVSS is applied as a high level voltage, and therefore the organic light-emitting diode of each pixel and the organic light-emitting diode OLEDd of each dummy pixel do not emit light.

[0147] The first and third repair control signals GE1 and GE3 transmitted to the repair driver DPXCb of each dummy pixel is applied as a high level voltage during the on-bias period Po, the reset period Pr, the compensation period Pth, and the scan period Ps, and the second repair control signal GE2 is applied as a low level voltage during the on-bias period Po, the reset period Pr, the compensation period Pth, and the scan period Ps.

[0148] Thus, the first repair transistor G1 of the repair driver DPXCb of each dummy pixel maintains a turned-off state during a non-light emission period (the on-bias period Po, the reset period Pr, the compensation period Pth, and the scan period Ps) so that a parasitic capacitor generated due to a laser short connection during resetting of the dummy pixel circuit and the threshold voltage compensation of the driving transistor can be separated.

[0149] In addition, the third repair transistor G3 of the repair driver DPXCb also maintains a turned-off state during the non-light emission period.

[0150] In addition, during the non-light emission period, the second repair transistor G2 of the repair driver DPXCb maintains a turned-on state to perform initialization, reset, and threshold voltage compensation in the same way as that of a typical pixel by using the capacitor Coled of the organic light-emitting diode.

[0151] However, during the non-light emission period, the second power source voltage ELVSS is applied as a high level voltage to the cathode of the organic light-emitting diode

OLEDd of the dummy pixel so that no current flow is generated toward the organic light-emitting diode.

[0152] Moreover, during the light emission period Pe, the first power source voltage ELVDD is applied as a high level voltage and the second power source voltage ELVSS is applied as a low level voltage.

[0153] Then, a current path is formed from the first power source voltage ELVDD to the organic light-emitting diode OLED, and the amount of driving current flowing through the current path corresponds to a data voltage that depends on the image data signal stored in the storage capacitor Cst1 during the light emission period Pe.

[0154] The organic light-emitting diode OLED of each pixel emits light with luminance that corresponds to the driving current.

[0155] The light emission period Pe is performed across the plurality of pixels of the display unit 10, and therefore the plurality of pixels substantially simultaneously emit light with a luminance corresponding to display an image.

[0156] During the light emission period Pe, the second and third repair control signals GE2 and GE3 transmitted to the repair driver DPXCb of each of the plurality of dummy pixels are applied as high level voltages and the first repair control signal GE1 is applied as a low level voltage.

[0157] Thus, during the light emission period Pe1, the second repair transistor G2 maintains a turned-off state so that a driving current can be prevented from flowing to the organic light-emitting diode OLEDd of the dummy pixel, thereby preventing the organic light-emitting diode OLEDd from emitting light.

[0158] In addition, the third repair transistor G3 of the repair driver DPXCb of each dummy pixel maintains a turned-off state during the light emission period Pe. However, the third repair control signal GE3 is transmitted as a low level voltage during a period from a time t1 to a time t2 before the start of the light emission period Pe. Thus, the third repair transistor G3 is turned on during the period from t1 to t2. That is, the third repair transistor G3 is turned on together with the first repair transistor G1 before the light emission period Pe, and the gate electrode is diode-connected. Thus, the driving voltage of an organic light-emitting diode of the previous frame stored in the repair line RL is initialized to the driving voltage of an organic light-emitting diode that is going to emit light. That is, when the third repair transistor G3 is turned on, a current flowing in the driving transistor M1 flows with the same characteristics of an organic light-emitting diode through the third repair transistor G3 so that the repair line RL may be initialized to the same voltage of the organic light-emitting diode of the light emission period.

[0159] Meanwhile, during the light emission period Pe, the first repair transistor G1 of the repair driver DPXCb of each dummy pixel is in the turned-on state and thus a driving current is transmitted to a light emission portion, that is, an organic light-emitting diode of a defective pixel having a driving failure among the plurality of pixels included in the pixel unit 101, through the repair line RL. Then, light can be emitted even through a pixel has experienced a driving failure, thereby preventing deterioration of luminance uniformity over than entire display unit.

[0160] FIG. 5 is a circuit diagram of a dummy pixel structure of a display device according to another exemplary embodiment.

[0161] A dummy pixel PDX1 according to the exemplary embodiment of FIG. 5 is formed of a driving circuit DPX1\_C and a light emission portion DPX1\_E of the dummy pixel.

[0162] The driving circuit DPX1\_C of the dummy pixel is connected with a repair line RL by a laser short when a defective pixel is detected in the pixel unit 101 of the display unit and is thus electrically connected with the light emission portion of the defective pixel.

[0163] In addition, the driving circuit DPX1\_C of the dummy pixel may be formed of a first driver, that is, a light emission driver DPX1\_Ca and a second driver, that is, a repair driver DPXc\_Cb.

[0164] The light emission driver DPX1\_Ca is a circuit that generates and transmits a driving current of a data voltage for light emission by activating the corresponding dummy pixel DPX1.

[0165] In addition, when a defective pixel is generated in the pixel unit 101, the repair driver DPX1\_Cb is a circuit that compensates for a failure of the defective pixel by being connected with the repair line by a laser short in the corresponding dummy pixel DPX1.

[0166] In the display device according to the exemplary embodiment, the structure of each of the plurality of pixels included in the pixel unit 101 is not illustrated, but each of the plurality of pixels may have the same structure as the dummy pixel DPX1, excluding the repair driver DPX1\_Cb. That is, each of the plurality of pixels forming the pixel unit to display an image according to an image signal has a structure in which the light emission driver DPX1\_Ca and the light emission portion DPX1\_E of the dummy pixel DPX1 are connected with each other.

[0167] In FIG. 5, the structure of the repair driver DPX1\_Cb and the light emission portion DPX1\_E of the dummy pixel DPX1 is the same as that of FIG. 3, and therefore no further description thereof will be provided.

[0168] In FIG. 5, the light emission driver DPX1\_Ca of the dummy pixel DPX1 will be described.

[0169] Referring to FIG. 5, the light emission driver DPX1\_Ca of the dummy pixel DPX1 includes a driving transistor A1, a switching transistor A2, a compensation transistor A3, a relay transistor A4, a sustain transistor A5, a storage capacitor Cst2, a sustain capacitor Chold, and a compensation capacitor Cth2.

[0170] The driving transistor A1 includes a gate electrode connected to a first node Q1, a first electrode connected to the first power source voltage ELVDD, and a second electrode connected to a third node Q3. The driving transistor A1 generates the corresponding driving current according to a data voltage that depends on an image data signal transmitted to the first node Q1 and transmits the driving current to an organic light-emitting diode of the light emission portion.

[0171] The switching transistor A2 includes a gate electrode connected to the corresponding scan line Sd among the plurality of scan lines, a first electrode connected to the corresponding data line Di among the plurality of data lines, and a second electrode connected to a fourth node Q4.

[0172] The switching transistor A2 is turned on by the scan signal S[d] having a pulse voltage of a gate-on level transmitted through the scan line Sd and transmits a data voltage D[i] that depends on the image data signal transmitted through the data line Di to the fourth node Q4. The fourth node Q4 is connected with the first electrode of the sustain capacitor Chold, and a second electrode of the sustain capacitor Chold is connected with a voltage supply line applying a predeter-

mined reference voltage  $V_{ref}$ . Thus, the sustain capacitor  $C_{hold}$  stores a voltage value according to a difference between the data voltage  $D[i]$  transmitted to the fourth node  $Q_4$  and the reference voltage  $V_{ref}$  to thereby perform the function of sustaining the data voltage  $D[i]$  according to the image data signal transmitted through the data line  $D_i$ .

[0173] The relay transistor  $A_4$  includes a gate electrode connected to a second control line  $GWL$ , a first electrode connected to the fourth node  $Q_4$ , and a second electrode connected to the second node  $Q_2$ . The relay transistor  $A_4$  is turned on by a second control signal  $GW$  having a pulse voltage of a gate-on level transmitted through the second control line  $GWL$  and transmits the data voltage  $D[i]$  applied to the fourth node  $Q_4$  and maintained therein to the second node  $Q_2$ .

[0174] The second node  $Q_2$  is connected with the first electrode of the storage capacitor  $C_{st2}$ , and a second electrode of the storage capacitor  $C_{st2}$  is connected to the first power source voltage  $ELVDD$ . Thus, the storage capacitor  $C_{st2}$  stores a voltage value according to a difference between the data voltage  $D[i]$  transmitted to the second node  $Q_2$  and the first power source voltage  $ELVDD$  during a predetermined period to thereby maintain the data voltage  $D[i]$  for a predetermined period.

[0175] Meanwhile, the compensation transistor  $A_3$  includes a gate electrode connected to a first control line  $GCL$ , a first electrode connected to the first node  $Q_1$ , and a second electrode connected to the third node  $Q_3$ .

[0176] The compensation transistor  $A_3$  is turned on by the first control signal  $GC$  having a pulse voltage of a gate-on level transmitted through the first control line  $GCL$  and diode-connects the gate electrode of the driving transistor  $A_1$  and the second electrode thereof. Thus, in the equation for calculating the amount of driving current that depends on the data voltage applied to the gate electrode terminal of the driving transistor  $M_1$ , the threshold voltage of the driving transistor is removed to eliminate and compensate for a threshold voltage deviation of the driving transistors of the pixels included in the display unit.

[0177] The compensation capacitor  $C_{th2}$  includes a first electrode connected to the first node  $Q_1$  and a second electrode connected to the second node  $Q_2$ . Since the compensation capacitor  $C_{th2}$  sustains a voltage difference at lateral ends thereof, a voltage value which depends on the threshold voltage of the driving transistor applied to the first node  $Q_1$  is maintained during a compensation period of the driving transistor.

[0178] Moreover, the sustain transistor  $A_5$  includes a gate electrode connected to the first control line  $GCL$ , a first electrode connected to the corresponding data line  $D_i$  among the plurality of data lines, and a second electrode connected to the second node  $Q_2$ .

[0179] The sustain transistor  $A_5$  is substantially simultaneously turned on with the compensation transistor  $A_3$  by the first control signal  $GC$  having a pulse voltage of a gate-on voltage transmitted through the first control line  $GCL$ . The sustain transistor  $A_5$  maintains a voltage of the second node  $Q_2$  by applying a predetermined voltage through the data line  $D_i$ .

[0180] The transistors forming the dummy pixel  $DPX_1$  of FIG. 5 are PMOS transistors, but are not limited thereto. The transistors may alternatively be formed as NMOS transistors.

[0181] A driving diagram for a display unit including the plurality of dummy pixels  $DPX_1$  having the circuit structure

of FIG. 5 and a plurality of pixels formed of the circuit structure of the dummy pixel  $DPX_1$ , excluding the repair driver  $DPX_1 Cb$ , is as shown in FIG. 6.

[0182] Referring to the timing diagram of FIG. 6, one frame period for displaying one image in the display unit 10 includes a reset period  $Pr_1$  including of a first reset period  $Pr_{1\_1}$  and a second reset period  $Pr_{1\_2}$ , a compensation period  $Pth_1$  for compensating a threshold voltage of the driving transistor of each pixel, a transmission period  $Pt$  for transmitting a data voltage according to the corresponding image data signal transmitted from a previous frame (hereinafter, referred to as a previous frame data voltage) to the second node  $Q_2$  for light emission, a scan period  $Ps_1$  for transmitting a data voltage corresponding to the present frame (hereinafter, referred to as a present frame data voltage) to each of the plurality of pixels, and a light emission period  $Pe_1$  for substantially simultaneous light emission of the plurality of pixels with a driving current that depends on the previous frame data voltage.